Most of the modular PXIe products adopt an FPGA based architecture, implementing the digital interfaces to the underlined hardware such as ADC/DAC, clock and memory management, trigger and sync, etc. The off-the-shelf feature-rich functionalities of the modules and the control (e.g. IQ modulator, function generators or queue system for the AWGs or advanced triggers and DAQs for the digitizers) are also implemented in the logic.

However, standard products typically do not have available resources for additional processing functions. Some applications require the use of custom on-board real-time processing which might not be covered by the comprehensive off-the-shelf functionalities of the standard hardware products. For these applications, Keysight supplies hardware products that provide the capability to program the on-board FPGA.

M3602A FPGA programming software is compatible with M3xxxA PXIe modular hardware products. M3602A provides the necessary tools to design, compile and program the FPGA of the module. M3xxxA offering is made of AWGs and digitizers that allow engineers to build onto the instrument's core capabilities or insert custom algorithms into the on-board FPGAs. This graphical design environment makes it easy to add customization required for emerging technologies, research and design while accessing the full performance and speed of the FPGA.

The M3602A FPGA Design Environment provides a graphical FPGA programmable environment that allows for customization capability. To take advantage of the M3602A software, it is important to order the -FP1 hardware option when purchasing the hardware. When configuring the hardware with option -FP1, select which FPGA wanted to be loaded on the hardware. FPGAs that needs to work with option -FP1 are bigger than those that come with the standard hardware.

The M3602A software enables non-expert and expert users to achieve high-performant solutions (e.g. loop control for DRFM, DPD* filtering for AWGs, data compression*, frequency masking, for data acquisition, etc.) based on the true parallelism of FPGA via a simple graphical interface.

The graphical interface:

* DPD Digital pre-distortion is used to pre-distort the signal going into a power amplifier to accommodate for non-linearity as the chip approaches the max power. Data compression is needed due to the high data throughput of current ADC and limitations of Data bandwidth from digitizer to host using PCIe x4 Gen2

Figure1 Avoid FPGA labyrinth

By design, the control of the main digital interfaces is kept out of the reach of the customizable area of the FPGA. This enables non-expert and expert users to be able to focus on the following tasks.

Non-expert users can (non-HDL programmers):

Expert-users can:

In addition to the faster compiling, it features hot programming capability where a module can be hot programmed with existing compiled code via PCIe without rebooting the instrument.

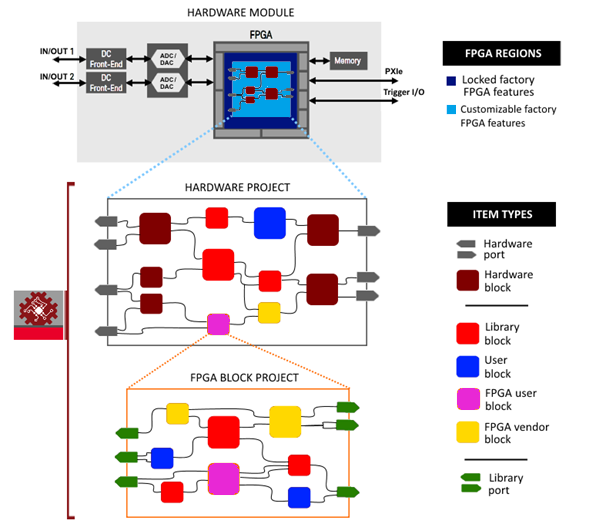

Referring to figure 2:

Figure2 M3602A workflow

Figure3 shows the relation between the different types of blocks available in M3602A. The control of the main digital interfaces is kept out of the reach (locked FPGA features in the FPGA project) of the customizable area of the FPGA

A Hardware project integrates some locked blocks such as the Hardware blocks and Hardware ports which are integrated into the control system of the digital interface. A description of the different functional blocks is included below:

Figure3 Ports, blocks and Project relations